Разработчики мультипроцессора Cell попытались отойти от обычной архитектуры. Результатами их усилий стали принципиально новая аппаратная модель и иная парадигма программирования.

Обсуждения совместной разработки процессора Cell начались при поддержке генеральных директоров Sony и IBM, причем первая компания фигурировала как поставщик контента, а вторая — как лидер в области информационных технологий и производства серверов. Так было положено начало сотрудничеству SCEI (Sony Computer Entertainment Incorporated) и IBM, к которым присоединилась Toshiba как партнер по разработке и массовому производству.

Летом 2000 года специалисты этих компаний обсудили в Токио общие концепции архитектуры нового процессора. В ходе встречи выяснилось, что традиционные архитектурные решения не могут дать той вычислительной мощности, на которую рассчитывала SCEI. Ее представители предлагали обсудить возможность тысячекратного превышения производительности PlayStation2 [1, 2]. Было решено сначала добиться в 100 раз большего быстродействия, а затем обеспечить его дальнейший рост.

На этой стадии к изучению новых подходов было привлечено исследовательское подразделение IBM Research Division. Были приняты во внимание технологические достижения IBM, в том числе современный 0,09-микронный процесс, применение кремния на изоляторе (Silicon-On-Insulator, SOI), диэлектриков low-k и медной разводки [3]. Новая архитектура должна была обеспечить создание цифрового центра развлечений, объединяющего достоинства широкополосных сетей, развлекательных систем и суперкомпьютеров. На встрече обсуждалось множество многоядерных вариантов — от обычных однокристальных мультипроцессоров (Chip Multiprocessor, CMP) до мультипроцессоров, управляемых потоком данных (dataflow-oriented).

К концу 2000 года была согласована архитектурная концепция, объединившая 64-разрядную архитектуру Power Architecture (www-106.ibm.com/developerworks/eserver/library/es-archguide-v2.html) с управлением потоками данных и «синергетическими» процессорами. Это должно было обеспечить требуемые интенсивность вычислений и энергетическую эффективность. После нескольких месяцев переговоров, связанных с обсуждением архитектуры и заключением контрактов, 9 марта 2001 года в Остине (штат Техас) официально открылся Проектный центр STI (SCEI-Toshiba-IBM). Он аккумулировал объединенные инвестиции в проект объемом примерно 400 млн долл.

Для того чтобы добиться успеха, компании предприняли целый ряд мер. Во-первых, использовался целостный подход, сводивший воедино архитектуру, аппаратную реализацию, системные структуры и модели программирования процессора. Во-вторых, на руководящие посты Проектного центра были приглашены сотрудники разных подразделений IBM. В-третьих, проект подразумевал использование множества гибких элементов (от перепрограммируемых синергетических процессоров до реконфигурируемых интерфейсов ввода-вывода), что позволяло обеспечить поддержку одним большим чипом нескольких системных конфигураций.

Проектный центр STI расположился в Остине, но жизненно важными для проекта были и следующие подразделения IBM: Рочестер (Миннесота), Йорктаун-Хейтс и Эндикотт (Нью-Йорк), Боблинген (Германия), Роли (Северная Каролина), Хайфа (Израиль), Альмаден (Калифорния), Бангалор (Индия), Ясу (Япония), Берлингтон (Вермонт). Кроме того, в городе Ист-Фишкилл (Нью-Йорк) действовала объединенная технологическая группа.

Цели и задачи проекта

Цели разработки нового процессора были следующими: добиться выдающейся производительности, особенно в игровых и мультимедийных приложениях; обеспечить живой отклик в режиме реального времени на действия пользователя и сетевые запросы; обеспечить применимость процессора на множестве платформ; подготовить процессор к выпуску в 2005 году.

Высокая производительность

Серьезный барьер на пути к увеличению производительности — повышение уровня латентности памяти, а также обусловленное ею ограничение на пропускную способность памяти. Проблема, известная также как «стена памяти» [4], состоит в том, что рост тактовой частоты процессоров не сопровождается достаточным снижением латентности динамической памяти DRAM. Следовательно, эффективная латентность DRAM увеличивается с каждым поколением. В процессоре с тактовой частотой несколько гигагерц латентность DRAM обычно измеряется сотнями тактов; в симметричных мультипроцессорах с общей памятью латентность основной памяти может составлять тысячи тактов.

Микропроцессор с обычной семантикой последовательного программирования способен выдержать лишь ограниченное число параллельных операций с памятью. В последовательной модели принято, что выполнение любой команды должно закончиться прежде, чем начнется выполнение следующей. Если при выборке команды или данных их не оказывается в кэш-памяти, то необходимо обращение к основной памяти, и обработка команды может продолжаться лишь в спекулятивной манере — предполагается, что доступ к основной памяти окажется успешным. Процессор должен также запомнить неспекулятивное состояние, чтобы продолжить обработку безопасным способом. Когда возникает зависимость от данных предыдущего обращения, которые отсутствовали в кэше, для продолжения работы требуется еще более глубокая спекуляция.

В обычных микропроцессорах очень редко одновременно осуществляются множество спекулятивных обращений к памяти. Это происходит по двум причинам. Во-первых, для спекулятивного продолжения вычислений нужен большой объем административной работы. Во-вторых, вероятность того, что полезная работа закончится спекулятивно, быстро уменьшается с ростом числа случаев, в которых процессор для продолжения работы должен предпринимать спекулятивную выборку данных. Если микропроцессор одновременно имеет, скажем, восемь 128-байтовых выборок из кэша (весьма оптимистичная оценка), а латентность памяти составляет 1024 такта, то максимально необходимая пропускная способность памяти составляет лишь 1 байт за такт. В такой системе ограничения пропускной способности памяти обусловлены ее латентностью, и увеличение пропускной способности за счет латентности может быть контрпродуктивным. Задача, следовательно, состоит в разработке такой архитектуры процессора, которая позволяет более эффективно использовать пропускную способность памяти за счет увеличения числа одновременных транзакций.

Мощность и плотность рассеиваемой мощности в процессорах CMOS выросли настолько, что мы опять испытываем необходимость в сложных методах охлаждения, которые, казалось бы, остались в биполярной эре [5]. Однако в потребительской электронике размеры корпуса, максимальные скорость обдува и температура выходящего из системы воздуха налагают фундаментальные ограничения на допустимую мощность — вне зависимости от технической изобретательности, направленной на повышение теплостойкости. Технологическая ситуация ухудшается по следующим причинам. Размеры транзисторов сегодня настолько малы, что туннелирование через затвор и подпороговые токи утечки препятствуют следованию законам масштабирования с постоянной площадью и сохранению плотности рассеиваемой мощности [6]. Кроме того, отсутствует альтернативная маломощная технология. Следовательно, наряду с ростом производительности необходимы средства повышения энергетической эффективности [7].

Еще один барьер к росту производительности обусловлен тем, что мы достигли точки убывающей приростной отдачи при ее повышении за счет дальнейшего увеличения тактовой частоты процессора и глубины конвейера [8]. Трудность состоит в том, что с ростом глубины конвейера увеличивается и латентность команд — вследствие дополнительной нагрузки от возрастающего числа его регистров-защелок. Таким образом, производительность, полученная благодаря увеличению частоты (и способность выдавать больше команд в единицу времени), должна превышать потери времени из-за роста латентности выполнения команд. Эти потери включают в себя временные слоты выдачи команд, которые нельзя использовать (поскольку существует зависимость от результатов предыдущих команд), и пустые затраты времени из-за неверного предсказания команд перехода.

Если из-за ограничений по мощности не удается в достаточной мере повысить частоту, то увеличение глубины конвейера и латентности выполнения команд может привести к снижению, а не к повышению производительности. Отметим: чем меньше команд за такт выдает процессор, тем успешнее он выдерживает повышение тактовой частоты. Следовательно, требуется разработать микроархитектуру процессора и такие его реализации, которые минимизируют глубину конвейера и смогут эффективно использовать доступные им слоты выдачи команд.

Отклик в режиме реального времени

С самого начала предполагалось, что процессор Cell должен быть максимально удобен для пользователя и наилучшим образом приспособлен для работы в Сети. Эта направленность «вовне» отличается от «внутренней» направленности процессора, характерной для эры пакетной обработки данных, когда главной заботой было обеспечение постоянной загрузки ЦП.

Кроме того, большинство устройств на базе этого процессора будут подключены к широкополосной сети Internet. На начальных этапах предполагалось смешение контента (реального или виртуального) из Internet с контентом традиционных игр и развлечений. Это требует одновременной поддержки как операционных систем реального времени, так и традиционных ОС, выполняющих приложения доступа к Internet. Живой отклик на сетевые запросы означает не только оптимизацию процессора для выполнения рабочих нагрузок, ориентированных на коммуникации. Подразумевается также, что он должен быть «отзывчив» к типам рабочих нагрузок, характерных для Internet. А поскольку Сеть поддерживает множество стандартов, например, разные стандарты потокового видео, необходимы гибкость и программируемость любой функции ускорения.

Наконец, вместе с возможностями совместного использования данных и вычислительных мощностей приходят проблемы защиты, конфиденциальности и управления правами доступа.

Применимость на многих платформах

Проект Cell стал ответом на потребность в процессоре для нового поколения развлекательных систем. Однако новая архитектура, ориентированная на игровые и мультимедийные приложения и специально разработанная для оптимального взаимодействия с пользователем и широкополосной сетью в режиме реального времени, может оказаться эффективной и в широком диапазоне приложений для «цифрового дома» и его «окрестностей». Архитектура BPA (Broadband Processor Architecture; www-306.ibm.com/chips/techlib/techlib.nsf/products/Cell.) рассчитана на долгую жизнь, выходящую далеко за рамки ее инкарнации в первом поколении процессора Cell. Для расширения области ее применения и появления сообщества разработчиков ПО, которое станет оптимизировать приложения для этой архитектуры, наряду с процессором первого поколения была разработана открытая (на базе Linux) среда разработки программного обеспечения.

Концепция и архитектура проекта

|

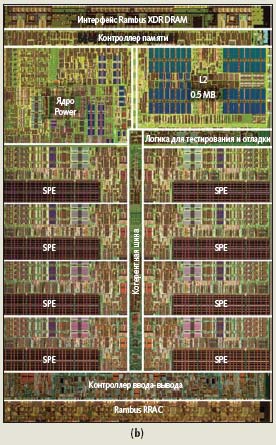

| Рис. 1. (a) Блок-схема процессора Cell и (b) фотография кристалла. Процессор Cell первого поколения содержит процессорный элемент PPE с ядром Power, кэши первого и второго уровня (L1 и L2), контроллеры интерфейсов шины и памяти, а также восемь синергических процессорных элементов SPE, каждый из которых имеет блок прямого доступа к памяти (DMA), локальную память (LS) и блок выполнения команд (SXU). Все элементы процессора соединены когерентной внутренней шиной. (Фотографию кристалла Cell предоставил Томас Уэй из подразделения IBM в Берлингтоне.) |

Архитектура Broadband Processor Architecture расширяет возможности 64-разрядной архитектуры Power Architecture благодаря использованию согласованно действующих дополнительных «синергетических» процессоров с прямым доступом к памяти (Direct Memory Access, DMA), механизмов синхронизации для связи с ними (управления потоками данных) и усовершенствований, нацеленных на управление в режиме реального времени. В состав процессора Cell первого поколения (рис. 1) входят двухпоточный процессорный элемент PPE (Power processor element), совместимый с 64-разрядной архитектурой Power Architecture и способный выдавать две команды за такт, восемь новых синергетических процессорных элементов SPE (synergistic processor element) [9], внутренний контроллер памяти и контроллер для конфигурируемого интерфейса ввода-вывода. Эти устройства связаны внутренней когерентной шиной EIB (element interconnect bus). Поддерживаются такие распространенные функции, как самопроверка при включении питания, встроенные механизмы отладки оборудования и мониторинг работы. Ключевые особенности концепции таковы.

- Высокая проектная частота (малое число затворов на такт). Благодаря этому процессор работает при низком напряжении и с небольшим энергопотреблением, сохраняя высокие тактовую частоту и производительность.

- Совместимость с архитектурой Power Architecture. Она обеспечивает привычные условия для программистов при виртуализации и поддержке нескольких операционных систем, а также возможность использовать опыт IBM, накопленный при проектировании и верификации симметричных мультипроцессоров.

- Использование архитектуры SIMD (Single Instruction Multiple Data — один поток команд и множество потоков данных). Это — одно из средств повышения производительности игровых/мультимедийных и научных приложений при повышенной энергетической эффективности. SIMD поддерживают как векторные мультимедийные расширения на PPE, так и система команд процессоров SPE.

- Применение экономичного компактного процессора PPE с высокой проектной частотой.

- Использование процессоров SPE для когерентного распределения нагрузки. SPE имеют локальную память, асинхронный когерентный прямой доступ к основной памяти и большие унифицированные файлы регистров. Это позволяет улучшить пропускную способность памяти, обеспечить новые уровни энергетической эффективности и производительности. SPE можно динамически конфигурировать для поддержки секретности и защиты контента.

- Применение внутренней широкополосной когерентной шины и памяти с высокой пропускной способностью. Они обеспечивают значительную производительность приложений с интенсивным обменом данными и внутренних взаимодействий между процессорными элементами. Когерентность шины позволяет PPE и SPE совместно задействовать единое адресное пространство, что повышает эффективность коммуникаций и упрощает программирование.

- Гибкость ввода-вывода с высокой пропускной способностью. Могут поддерживаться несколько вариантов организации системы, в том числе однопроцессорная конфигурация с двумя интерфейсами ввода-вывода и когерентная двухпроцессорная конфигурация, которая не требует дополнительных коммутирующих устройств для соединения процессоров.

- Полностью настраиваемая модульная реализация. Она позволяет максимизировать удельную производительность на единицу мощности и удельную производительность на единицу площади подложки, а также облегчить проектирование производных продуктов.

- Расширенная поддержка управления потреблением мощности и тепловыделением чипа, производственных испытаний, анализа производительности, отладки оборудования и программного обеспечения.

- Применение эффективной и дешевой технологии размещения элементов в корпусе.

- Использование высокопроизводительного 0,09-микронного технологического процесса «кремний на изоляторе» с низким энергопотреблением.

Высокая проектная частота и пониженное напряжение питания

При обеспечении максимальной производительности с заданными площадью подложки и потребляемой мощностью одна из проблем состоит в согласованной оптимизации площади чипа, проектной частоты и рабочего напряжения процессора. Поскольку при снижении напряжения питания эффективность работы процессора резко увеличивается (быстрее, чем по квадратичному закону), при заданной мощности можно повысить производительность за счет роста числа транзисторов (что ведет к увеличению размеров чипа) и снижения питающего напряжения.

На практике рабочее напряжение имеет минимум (часто определяемый встроенной статической памятью RAM), при котором чип перестает правильно функционировать. Минимальное рабочее напряжение, а также размеры чипа, коэффициенты коммутации (связанные с процентом транзисторов, рассеивающих коммутируемую мощность на данном такте) и технологические параметры (такие как емкостные токи или токи утечки) определяют рассеиваемую мощность процессора как функцию его частоты. И наоборот, при заданных энергопотреблении, технологии, минимальном рабочем напряжении и коэффициенте коммутации можно оценить максимальную рабочую частоту для данного размера чипа.

Достижения этой частоты следует добиваться, если это возможно без такого снижения эффективности проекта, что проще было бы воспользоваться меньшим чипом, работающим при более высоком напряжении питания. Оптимально сбалансированный процессор должен работать при минимальном напряжении, при котором электрические цепи сохраняют работоспособность, и с максимальной для этого напряжения частотой. Потребляемая чипом мощность не должна превышать мощность, допустимую для устройства, в котором он применяется. Применительно к процессору Cell задача состояла в том, чтобы длительность такта оказалась меньше задержки в цепочке, состоящей из десяти инверторов с коэффициентом разветвления 4 (10 FO4). Позднее (когда стало ясно, что иначе проигрыш в занимаемой площади и потребляемой мощности окажется значительным) этот показатель был увеличен до 11 FO4.

Совместимость с Power

Архитектура Broadband Processor Architecture полностью совместима с 64-разрядной Power Architecture. Ее реализация в процессоре Cell вобрала в себя все новшества технологии Power, такие как поддержка виртуализации и страниц большого размера. Опора на проверенную архитектуру и фокусировка внимания на аспектах, способных дать новые преимущества, позволила закончить сложный проект в сжатые сроки. Кроме того, совместимость с Power Architecture обеспечивает перенос на процессор Cell имеющегося ПО, в том числе операционной системы. Для обеспечения полной производительности Cell требуется дополнительная работа, но приложения Power могут выполняться на нем без изменений.

Архитектура SIMD

Процессор Cell использует архитектуру SIMD (Single Instruction Multiple Data — один поток команд и множество потоков данных) в векторных модулях PPE и SPE. Модули SIMD продемонстрировали свою эффективность при ускорении мультимедийных приложений. Теперь такие модули применяются во всех основных процессорах для ПК, поэтому идет процесс совершенствования ПО, в том числе компиляторов, которые генерируют SIMD-команды для кода, написанного без явного их использования.

Благодаря расширениям SIMD в PPE и SPE сильно упрощаются разработка и перенос программного обеспечения на Cell. Как правило, приложение задумывается как однопоточное, и SIMD не используется. Первый шаг к повышению производительности может состоять в применении SIMD на PPE, а типичный второй шаг — в использовании SPE. Хотя архитектуры SIMD на SPE и PPE отличаются друг от друга, у них много общего. Программисты могут строить программы, имеющие достаточную производительность на PPE и, после перекомпиляции, на SPE. Поскольку в однопоточном режиме PPE обеспечивает такую среду отладки и тестирования, которая все еще является наиболее знакомой для программистов, многие из них предпочитают именно этот подход к программированию Cell.

Процессорный элемент PPE

Процессорный элемент PPE (рис. 2) представляет собой 64-разрядное ядро, совместимое с архитектурой Power Architecture. Оно оптимизировано для достижения проектной частоты и повышения энергетической эффективности. Его проектная частота 11 FO4 согласуется с частотами SPE, но глубина конвейера составляет лишь 23 стадии. Это значительно меньше, чем можно было бы ожидать от продукта, который выполняет стадию почти в два раза быстрее, чем более ранние [10, 11].

Микроархитектура и план размещения элементов процессора лишены длинных соединений, что сокращает задержки передачи данных, а потому данное устройство можно назвать «процессором с короткой разводкой». PPE упрощен по сравнению с более новыми процессорами, способными выдавать четыре команды за такт с возможностью изменения их последовательности (four-issue out-of-order processors). PPE может выдавать две команды за такт, и он динамически не переупорядочивает их при выдаче (in-order issue).

Ядро чередует команды от двух вычислительных потоков, выполняющихся одновременно. Это позволяет оптимизировать использование слотов выдачи команд, сохранить максимальную эффективность процессора и уменьшить глубину конвейера. Простые арифметические операции выполняются и отправляют далее свои результаты за два такта. Благодаря режиму отложенного выполнения на конвейере операций с фиксированной запятой команды загрузки также завершаются и отправляют свои результаты за два такта. Команда двойной точности с плавающей запятой выполняется за десять тактов.

PPE поддерживает обычную иерархию кэш-памяти; имеются кэши первого уровня для команд и данных емкостью по 32 Кайт и кэш-память второго уровня емкостью 512 Кбайт. Кэш второго уровня и кэши преобразования адресов используют таблицы управления заменой, чтобы разрешить программе направлять данные из определенных диапазонов адресов в конкретное подмножество кэша. Такой механизм позволяет блокировать данные в кэше, если размер диапазона адресов равен размеру множества. Он может служить и для предотвращения перезаписи данных в кэше: данные, применяемые только один раз, направляются в определенное множество кэша. Все это повышает эффективность процессора и усиливает контроль над процессором, осуществляемый в масштабе реального времени.

Процессор обеспечивает два одновременных потока выполнения и может рассматриваться как двухпроцессорный мультипроцессор с общим потоком данных. Это позволяет ПО воспринимать его как два независимых процессора. Продублированы все видимые состояния, в том числе видимые регистры и регистры специального назначения (за исключением регистров, имеющих дело с ресурсами на уровне системы, такими как логические разделы, память и управление потоками). Невидимые для программиста ресурсы (типа кэшей и очередей) обычно используются обоими потоками совместно. Исключение составляют те случаи, когда ресурс невелик или может существенно повысить производительность многопоточных приложений.

Процессор состоит из трех узлов (рис. 2a). Узел команд IU (instruction unit) отвечает за выборку, дешифровку, выдачу и завершение команды, а также за выполнение команд перехода. Узел операций с фиксированной запятой XU (fixed-point execution unit) выполняет все команды с фиксированной запятой и команды загрузки/сохранения. Узел векторно-скалярных команд VSU (vector scalar unit) отвечает за векторные команды и команды с плавающей запятой.

Узел команд IU за один такт выбирает из каждого потока четыре команды в буфер команд и отправляет команды из этого буфера по назначению. После дешифровки и проверки зависимостей команды выдаются на узел выполнения по две за такт. Для прогнозирования результата команды перехода служит таблица истории переходов 4 Кбит х 2 бит с шестью битами глобальной истории на поток. Узел IU может выдавать до двух команд за такт.

При такой «сдвоенной» выдаче возможны любые комбинации, кроме двух команд к одному и тому же узлу, а также следующих исключений. Простая векторная, комплексная векторная, векторная с плавающей запятой и скалярная с плавающей запятой арифметические команды не могут быть сдвоены с командой того же типа (например, не допускается выдача простой векторной команды в одном такте с комплексной векторной). Однако эти команды могут быть сдвоены с любой формой команды загрузки/сохранения, перехода с фиксированной запятой или перестановки элементов вектора. Очередь готовых к выдаче команд в узле VSU отделяет конвейеры векторных команд и команд с плавающей запятой от остальных конвейеров. Это позволяет выдавать такие команды вне очереди других команд.

Узел XU состоит из двух файлов регистров общего назначения 32x64 бит (по одному на поток), блока выполнения команд с фиксированной запятой и блока загрузки/сохранения. В последний входят кэш данных первого уровня, кэш преобразования адресов, восьмиэлементная очередь кэш-промахов и 16-элементная очередь хранения. Он поддерживает неблокирующий кэш данных первого уровня, который позволяет процессору обращаться к другой области кэш-памяти даже в процессе замены блока, вызвавшего кэш-промах (hit under miss cache).

Узел VSU состоит из двух файлов регистров 32x64 бит (по одному на поток) и конвейера двойной точности с десятью стадиями. Узел работает со 128-разрядным потоком данных. Он имеет четыре подузла для выполнения простых и комплексных векторных операций, операций одинарной точности с плавающей запятой и операций перестановки. В нем имеются два 32-элементных 128-разрядных векторных файла регистров (по одному на поток), а все команды являются 128-разрядными SIMD-командами с изменяющейся шириной элементов (2x64, 4x32, 8x16, 16x8 и 128x1 разрядов).

Процессорный элемент SPE

В процессорном элементе SPE [9] реализована новая архитектура системы команд, энергопотребление и производительность которой оптимизированы для вычислительных и мультимедийных приложений. SPE (рис. 3) работает с локальной памятью объемом 256 Кбайт, которая хранит команды и данные. Они передаются между этой и системной памятью с помощью асинхронных когерентных команд прямого доступа, которые выполняются блоком управления потоком данных, входящим в состав любого SPE.

Каждый SPE поддерживает до 16 ожидающих выполнения команд прямого доступа к памяти (DMA). В этих когерентных командах применяются такие же, как в PPE, преобразование адресов и защита, управляемые таблицами страниц и сегментов из архитектуры Power Architecture, поэтому адреса можно передавать между PPE и SPE. Вследствие этого операционная система способна использовать общую память и согласованно управлять всеми системными ресурсами.

Блок DMA может быть запрограммирован одним из трех способов: при помощи команд SPE, которые вставляют в очереди команды прямого доступа к памяти; путем подготовки в локальной памяти списка команд для пересылки содержимого разрозненных участков памяти (scatter-gather DMA) и выдачи единого списка команд DMA; с помощью вставки команд в очередь DMA другого процессора (с соответствующими привилегиями) и применения команд сохранения или записи DMA. Для удобства программирования (чтобы разрешить транзакции DMA типа «локальная память — локальная память») локальная память отображается на карту памяти процессора. Однако при кэшировании эта память не является в системе когерентной.

Появление локальной памяти вводит новый уровень иерархии памяти — в дополнение к регистрам, которые обеспечивают локальное хранение данных в большинстве процессорных архитектур. Это обеспечивает механизм борьбы с проблемой «стена памяти» (memory wall), поскольку позволяет одновременно выполнять множество транзакций с памятью без глубокой спекуляции, которая сильно снижает эффективность других процессоров. Латентность основной памяти приближается к 1 тыс. тактов, поэтому те несколько тактов, которые нужны для настройки команды DMA при обращении к ней, становятся вполне приемлемой дополнительной нагрузкой. Очевидно, что такая организация процессора удобна для обработки мультимедийных потоков. А поскольку локальная память достаточно велика для хранения большего, чем просто ядро потока (streaming kernel), возможна поддержка самых разных моделей программирования.

Локальная память — самый крупный компонент SPE, поэтому была очень важна ее эффективная реализация [12]. Для минимизации площади использована однопортовая ячейка SRAM. Локальная память имеет узкий (128-разрядный) и широкий (128-байтовый) порты чтения и записи. Это обеспечивает высокую производительность, хотя она и должна выступать в роли арбитра по отношению к операциям чтения, записи, выборки команд, загрузки и сохранения с прямым доступом. Широкий порт служит для прямого чтения и записи в память, а также для (упреждающей) выборки команд.

Поскольку типичная 128-байтовая операция прямого чтения/записи требует 16 тактов процессора для пересылки данных по внутренней когерентной шине (даже когда операции прямого чтения/записи выполняются без ограничений на пропускную способность), семь из каждых восьми тактов остаются доступными для операций загрузки, сохранения и выборки команд. Аналогичным образом команды выбираются по 128 байтов за раз, и нагрузка на локальную память остается минимальной. Наивысший приоритет отдан командам DMA, за которыми следуют операции загрузки и сохранения, а операция упреждающей выборки команды выполняется, когда есть свободный такт. Существует специальная команда «без операции», позволяющая при необходимости принудительно обеспечить доступность слота для выборки команды.

Блоки выполнения операций в SPE работают со 128-разрядным потоком данных. Достаточно большой файл регистров из 128 элементов позволяет компилятору переупорядочить команды и компенсировать латентность их выполнения. Имеется только один файл регистров, а все команды являются 128-разрядными SIMD-командами с изменяющейся шириной элемента (2x64, 4x32, 8x16, 16x8 и 128x1 разрядов).

За один такт может быть выдано до двух команд; один слот выдачи команды поддерживает операции с плавающей и фиксированной запятой, а другой обеспечивает загрузку/сохранение, операции перестановки байтов и перехода. Простые операции с фиксированной запятой занимают два такта, а команды одинарной точности с плавающей запятой и команды загрузки требуют шести тактов. Поддерживаются также двухпоточные SIMD-команды двойной точности с плавающей запятой, но максимальная скорость их выдачи составляет семь тактов на команду. Все остальные команды полностью конвейеризованы.

Для того чтобы ограничить дополнительную нагрузку на оборудование, вызванную прогнозированием ветвлений, программист или компилятор могут «подсказать» переход. Команда подсказки перехода уведомляет оборудование об адресе предстоящей команды перехода и его целевом адресе. Оборудование (в предположении, что доступны слоты локальной памяти) заранее выбирает по меньшей мере 17 команд по целевому адресу перехода. Для уменьшения числа ветвлений в коде можно использовать поразрядную команду выбора с тремя источниками.

Область управления занимает лишь 10-15% ядра SPE общей площадью 10 мм2, но несколько приложений все же достигают почти пиковой производительности на этом процессоре. Весь SPE занимает 14,5 мм2 и рассеивает лишь несколько ватт при работе на частоте несколько гигагерц.

Когерентная транспортная подсистема и память с высокой пропускной способностью

В Cell первого поколения пропускная способность памяти без больших системных издержек была улучшена с помощью памяти нового поколения Rambus XDR DRAM (www.rambus.com/products/xdr), которая обеспечивает передачу данных со скоростью 12,8 Гбит/с по 32-разрядному каналу. Процессор Cell поддерживает два таких канала с общей пропускной способностью 25,6 Гбит/с. Поскольку пропускная способность внутренней транспортной подсистемы чипа почти на порядок выше (96 байт за такт при пиковой нагрузке), между его блоками почти не возникают конфликты при операциях прямого доступа к памяти.

Ввод-вывод

Для построения эффективных двухпроцессорных систем, а также систем с подключенным к вводу-выводу высокопроизводительным акселератором или чипом системного интерфейса процессор Cell оснащен конфигурируемым интерфейсом ввода-вывода с высокой пропускной способностью. На физическом уровне семь передающих и пять приемных однобайтовых каналов Rambus RRAC FlexIO [13] могут быть выделены для двух отдельных логических интерфейсов. Один из них допустимо сконфигурировать для работы в качестве когерентного интерфейса. Таким образом, Cell поддерживает несколько системных конфигураций с высокой пропускной способностью (рис. 4).

Модели программирования

Удобству программирования процессора Cell уделялось огромное внимание уже на самых ранних этапах проекта.

Особенностью процессора Cell является наличие локальной памяти, которой программное обеспечение должно управлять. Это — одна из самых трудных задач для программистов, но и самый большой резерв для роста производительности приложений. Когда-нибудь с задачей управления памятью будет эффективно справляться компилятор, но сейчас она, прежде всего, ложится на плечи программистов или авторов библиотек.

|

| Рис. 4. Варианты конфигурации системы Cell: a) Базовая конфигурация для небольших систем; b) Двухпроцессорный симметричный мультипроцессор без дополнительных коммутирующих устройств для соединения процессоров; c) четырехпроцессорный симметричный мультипроцессор. (IOIF: интерфейс ввода-вывода; BIF: интерфейс широкополосной сети.) |

Еще одна особенность процессора, влияющая на модель программирования, — возможность обрабатывать потоки данных с помощью SIMD-команд. Программисты могут игнорировать эту особенность, но тогда они лишатся солидной прибавки производительности. SPE можно программировать как обычный скалярный процессор, если приложение с трудом поддается векторизации для SIMD. Особенности SIMD в SPE используются программистами и поддерживаются компиляторами почти так же, как блоки SIMD в процессорах PC. Соответственно, они приносят аналогичные выгоды.

SPE отличается от обычных микропроцессоров и по ряду других показателей. Наиболее значительные различия проявляются в размере файла регистра (128 элементов), в способе обработки переходов (и сокращения их количества) и в некоторых командах, позволяющих программному обеспечению выполнять арбитражные функции в локальной памяти и выдавать команды. Такие особенности SPE могут учитываться и эффективно использоваться компилятором. Программист, желающий получить максимальную производительность, способен извлечь из них пользу, но необходимость программировать SPE на ассемблере почти никогда не возникает.

Кроме того, в отличие от обычных процессоров, SPE в каждый момент поддерживает лишь один программный контекст. Этот может быть поток в приложении (режим задачи) или поток в привилегированном режиме (режим супервизора), расширяющий возможности операционной системы. Cell поддерживает виртуализацию и позволяет нескольким операционным системам выполняться одновременно над уровнем ПО виртуализации, работающего в состоянии «гипервизора». Для поддержки возможностей гипервизора можно применять SPE. То, что SPE поддерживает только один контекст, будет использоваться операционной системой. Большинство программистов однопроцессорных машин не всегда знают, что операционная система периодически отбирает у их приложений время выполнения (и содержимое кэша). Так же они могут не осознавать, что SPE управляются операционной системой, которая выполняется на другом процессоре.

Богатый выбор средств межпроцессорной связи и перемещения данных Cell позволяет применять самые разные модели программирования. Например, имеющиеся приложения могут задействовать SPE относительно прозрачным образом: использовать модель выгрузки функций, в которой код для SPE обеспечивает ускорение библиотечных функций, весьма важных для производительности.

Поддержка многих из моделей программирования на языке высокого уровня (типа Cи) сыграла важную роль в разработке архитектуры Cell. Для удобства программирования в архитектуру Cell внесены многочисленные изменения. Перед принятием окончательных решений по архитектуре и реализации Cell были написаны, проанализированы и проверены на функциональном имитаторе тестовые программы, библиотеки функций, расширения операционной системы и приложения.

***

Пока рано определять успешность процессора Cell, сравнивая производительность широкого спектра программ. Однако имеются эмпирические свидетельства того, что в самых разных приложениях (от обработки изображений и трассировки лучей до мультимедийных кодеков и потоковой криптографии) можно достичь почти пиковой производительности.

ЛИТЕРАТУРА

- K. Kutaragi, M. Suzuoki, T. Hiroi, etc. A Micro Processor with a 128b CPU. 10 Floating-Point MACs, 4 Floating-Point Dividers and an MPEG2 Decoder, ISSCC Digest of Technical Papers.— February 1999, pp. 256-257.

- A. Kunimatsu, N. Ide, T. Sato, etc. Vector Unit Architecture for Emotion Synthesis, IEEE Micro 20, No. 2, 40-47 (March-April 2000).

- H. S. Yang, R. Malik, S. Narasimha, etc. Dual Stress Liner for High Performance Sub-45-nm Gate Length SOI CMOS Manufacturing, Proceedings of the 2004 IEEE International Electron Devices Meeting.— December 2004, pp. 1075-1078.

- W. Wulf and S. McKee. Hitting the Memory Wall: Implications of the Obvious, ACM Computer Architecture News 23, No. 1, 20-24 (March 1995).

- U. Ghoshal and R. Schmidt. Refrigeration Technologies for Sub-Ambient Temperature Operation of Computing Systems, ISSCC Digest of Technical Papers. — February 2000, pp. 216-217.

- R. D. Isaac. The Future of CMOS Technology, IBM J.Res. & Dev. 44, No. 3, 369-378 (May 2000).

- H. Peter Hofstee. Power Efficient Processor Architecture and the Cell Processor, Proceedings of the 11th Conference on High Performance Computing Architectures. — February 2005, pp. 258-262.

- V. Srinivasan, D. Brooks, M. Gschwind, etc. Optimizing Pipelines for Power and Performance, Conference Proceedings of the 35th Annual IEEE/ACM International Symposium on Microarchitecture.— 2002, pp. 333-344.

- B. Flachs, S. Asano, S. H. Dhong, etc. The Microarchitecture of the Streaming Processor for a CELL Processor, Proceedings of the IEEE International Solid-State Circuits Symposium.— February 2005, pp. 184-185.

- С J. Anderson, J. Petrovick, J. M.Keaty, etc. Physical Design of a Fourth-Generation POWER GHz Microprocessor, ISSCC Digest of Technical Papers. — February 2001, pp. 232-233.

- J. Clabes, J. Friedrich, M. Sweet, J. DiLullo, etc. Design and Implementation of the POWER5 Microprocessor, Proceedings of the 41st Design Automation Conference.— 2004, pp. 670-672.

- T. Asano, T. Nakazato, S. Dhong,, etc. A 4.8GHz Fully Pipelined Embedded SRAM in the Streaming Processor of a CELL Processor, Proceedings of the IEEE International Solid-State Circuits Symposium.— February 2005, pp. 486-487.

- K. Chang, S. Pamarti, K. Kaviani, etc. Clocking and Circuit Design for a Parallel I/O on a First Generation CELL Processor, Proceedings of the IEEE International Solid-State Circuits Symposium.— February 2005, pp. 526-527.

Джеймс Кэйхел (jakahle@us.ibm.com) — почетный сотрудник IBM, директор по технологиям Проектного центра STI подразделения IBM Systems and Technology Group. Майкл Дэй (mnday@us.ibm.com) — главный архитектор системного ПО. Питер Хофсти (hofstee@us.ibm.com) — член архитектурной группы Cell и главный архитектор процессорного элемента SPE для процессора Cell. Чарльз Джонс (crjohns@us.ibm.com) — старший технический сотрудник. Теодор Маерер (maeurer@us.ibm.com) — менеджер по организации ПО. Дэвид Шиппи (shippy@us.ibm.com) — главный архитектор процессорного элемента PPE для процессора Cell.

J. A. Kahle, M.N. Day, H.P. Hofstee, C.R. Johns, T.R. Maeurer, D. Shippy, Introduction to the Cell multiprocessor. IBM Journal of Research and Development, Vol. 49 № 4/5, 2005. Copyright 2005, International Business Machines Corporation. All rights reserved. Reprinted with permission.