Клуб стран, ставших обладателями систем с уровнем производительности, ранее доступным только сверхдержавам, значительно расширился, а присутствие на высших позициях в рейтинговом списке Top500 стало престижным. Однако в ряде западных стран быстро оценили последствия кажущейся дешевизны, и им хватило мудрости не увлекаться коммерчески доступными технологиями, особенно в системах для решения задач, требующих интенсивного и неупорядоченного доступа к памяти и поэтому выделяемых в отдельный класс (DIC, Data-Intensive Сomputing). Каким должен быть суперкомпьютер для решения DIC-задач?

Клуб стран, ставших обладателями систем с уровнем производительности, ранее доступным только сверхдержавам, значительно расширился, а присутствие на высших позициях в рейтинговом списке Top500 стало престижным. Однако в ряде западных стран быстро оценили последствия кажущейся дешевизны, и им хватило мудрости не увлекаться коммерчески доступными технологиями, особенно в системах для решения задач, требующих интенсивного и неупорядоченного доступа к памяти и поэтому выделяемых в отдельный класс (DIC, Data-Intensive Сomputing). Каким должен быть суперкомпьютер для решения DIC-задач?

«Отрезвление» после недолгого безоглядного увлечения коммерчески доступными технологиями в суперкомпьютеростроении в развитых странах происходило по-разному. Так, в Японии быстро осознали ценность уже существовавших технологий векторных суперкомпьютеров, а в США, где доминировали кластеры и за 10-15 лет произошло разрушение инфраструктуры проведения исследований и разработок в области заказных и полузаказных суперкомпьютеров — главной составляющей суперкомпьютерной отрасли, — значительно позже был предпринят ряд чрезвычайных мер по ее восстановлению. Аналогичную полосу увлечения кластерами сегодня проходит и Россия, хотя в США давно уже осознали последствия легких побед при использовании кластерных технологий, правда после того, как Япония преподала этой стране урок на тему, каким должен быть суперкомпьютер для решения стратегически важных для государства задач, обычно выделяемых в отдельный класс вычислений с интенсивной обработкой данных (Data-Intensive Сomputing, DIC). Была создана многопроцессорная векторная система Earth Simulator, лишившая США на несколько лет лидерства в области высокопроизводительных вычислений.

Сегодня уже очевидно, что кластеры весьма ограничены по своим возможностям в сравнении с «настоящим суперкомпьютером», немыслимым без полностью заказных (то есть создаваемых специально и не доступных на открытом рынке) и полузаказных технологий. Такая техника будущего сейчас создается по крупным федеральным программам ряда стран, в частности в США к началу следующего десятилетия ожидается появление суперкомпьютеров Cray Baker, Granit и Murble, IBM PERCS, а переходные системы такого класса появились уже в этом году: IBM Roadrunner и системы Cray XT5, XT5h и XMT. В России соответствующие работы также ведутся, но пока в гораздо меньшем масштабе.

Что же произошло за последнее время в области коммерчески доступных технологий построения высокопроизводительных систем после сравнительно недолгого периода их достаточно успешного применения? Заметим, что мы не предлагаем отказываться от этих технологий, но обращаем внимание на необходимость проявлять больше осторожности и здравого смысла при их продвижении для решения всех возможных задач, включая и задачи обеспечения национальной безопасности.

Основные изменения в области коммерчески доступных технологий — это появление многоядерных микропроцессоров и гетерогенности (разнородности) как ядер, так и собственно микропроцессоров. Пиковая производительность многоядерных микропроцессоров стала увеличиваться пропорционально количеству ядер, но, к сожалению, реальная производительность одного ядра, развиваемая на обычных MPI-программах, стала резко уменьшаться. В целом многоядерность не позволяла до недавнего времени добиться ожидаемой эффективности микропроцессоров, и причина этого заключается в слабых интерфейсах с памятью и коммуникационной сетью, производительность которых и раньше, даже при одном ядре, была недостаточной.

Тем не менее многоядерность и гетерогенность справедливо считаются великими событиями, открывающими новую эру в суперкомпьютинге, но надо научиться ими пользоваться, для чего могут понадобиться новые аппаратные решения в организации как интерфейсов и серверных плат, так и коммуникационных сетей, а главное — новые вычислительные модели и программное обеспечение. В целом в работах этого направления при создании высокопроизводительных систем, для которых стало применяться название псевдокоммерческий суперкластер, наблюдается смешивание старых кластерных технологий и новых архитектурно-программных решений. Катализатором этого процесса являются многоядерные микропроцессоры с количеством ядер, пока равным 4-8, а через несколько лет — с сотней ядер и несколькими сотнями аппаратных тредовых устройств, по нескольку в одном ядре.

Оптимальное использование многоядерного или многоядерно-мультитредового микропроцессора, как при создании, так и при использовании суперкластера, предполагает знание не только его пиковых характеристик, но и особенностей его реального поведения при разных нагрузках, что стимулировало во всем мире массу исследований оценочного тестирования этих изделий. Не стала исключением и данная работа, в которой исследуется фрагмент суперкластера на базе четырехпроцессорных плат с четырехъядерными микропроцессорами Barcelona и сетью Infiniband. Такая конфигурация интересна с точки зрения возможности ее использования для построения макета разрабатываемого отечественного суперкомпьютера стратегического назначения (CКСН). Основное свойство, которое хотелось бы видеть в СКСН, выполняющих задачи интенсивной обработки данных, — это нечувствительность (толерантность) к задержкам выполнения операций регулярного и нерегулярного доступа к памяти, а также операций с коммуникационной сетью. Свойство толерантности важно не только для решения обозначенных задач — потеря реальной производительности из-за неэффективности работы с памятью и сетью является сегодня главной бедой современных систем на базе многоядерных микропроцессоров.

Суперкластер на микропроцессорах Barcelona

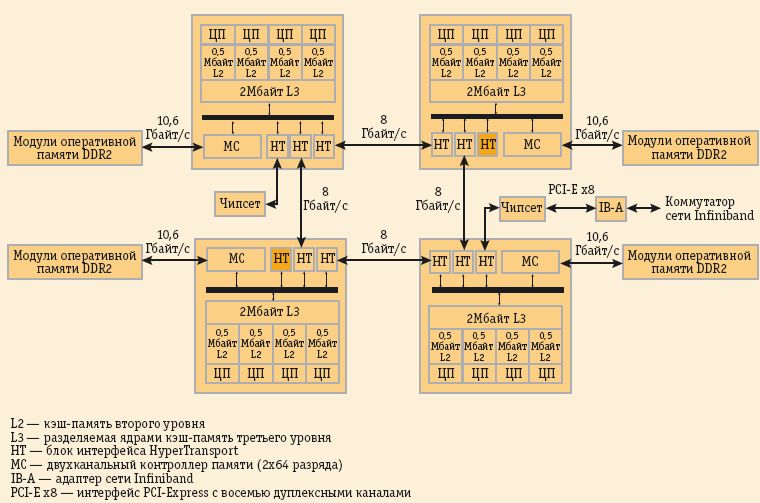

Суперкластер Barcelona состоит из четырех узлов, объединенных сетью Infiniband 4X DDR и размещенных на плате Supermicro AS-1041M-T2 (рис. 1). Каждый узел содержит четыре четырехъядерных процессора AMD Opteron 8350 (Barcelona) и 16 Гбайт оперативной памяти (возможна установка 64 Гбайт).

Пиковая производительность одного ядра микропроцессора определяется исходя из того, что имеются два блока (FADD и FMUL, блоком деления пренебрегаем), каждый из которых может выдавать результаты двух операций за такт, поскольку эти блоки 128-разрядные. При тактовой частоте 2 ГГц пиковая производительность ядра составит 8 GFLOPS, а пиковая производительность одного процессора с четырьмя ядрами будет в четыре раза больше.

В кластере для соединения узлов используется коммуникационная сеть Infiniband 4x DDR: сетевой адаптер (IB-A, рис. 1) — Mellanox MT2508 InfiniHost III (двухпортовый); коммутатор сети (IB-Switch) SBM-IBS-001 (чипсет Mellanox InfiniScale III, 4x DDR, неблокируемый, 10 внешних и 10 внутренних портов). Время установки соединения одного порта с другим — 160 нс. Пиковая дуплексная пропускная способность одного порта с учетом 10-битового кодирования байта — 2 Гбайт/c, которая определяется исходя из того, что один SDR дуплексный битовый канал (lane) работает на частоте 2,5 ГГц, а для DDR тактовая частота вдвое выше. Таким образом, получаем дуплексную сигнальную (на физическом уровне) пропускную способность одного канала — 5 Гбит/с, а для четырех — 20.

Дуплексная пропускная способность для двух портов в 4 Гбайт/с означает, что одновременно в одном и другом направлении можно передавать данные с пропускной способностью в 4 Гбайт/с. В этой статье мы будем использовать еще термин агрегатная пропускная способность, который означает сумму односторонних пропускных способностей; в данном случае она равна 8 Гбайт/с. Сетевой адаптер IB-A подключен через порт PCI-Express x8, его дуплексная пропускная способность равна 2 Гбайт/с, а агрегатная пропускная способность — 4 Гбайт/с. Интерфейс HyperTransport, к которому подключен мост HT-PCI-E, имеет дуплексную пропускную способность 4 Гбайт/с, что вдвое больше, чем у PCI-E x8.

Некоторые измерения на кластере Barcelona были проведены для двух узлов с оборудованием Infiniband 4x QDR. Для этого оборудования все характеристики пропускной способности были удвоены. Для сравнения в работе оценивались также следующие варианты:

-

один узел с двумя четырехъядерными микропроцессорами Clovertown/2,3 ГГц;

-

кластер МВС 50К МСЦ РАН с двумя четырехъядерными микропроцессорами Clovertown/3,0 ГГц в каждом узле и сетью Infiniband 4x DDR.

Регулярная и нерегулярная работа с памятью

Проблема медленной работы с памятью известна давно, но ход развития микроэлектронных технологий был таков, что пока эта проблема только ужесточается. Наибольшей популярностью пользуются два следующих подхода к ослаблению влияния этой проблемы: уменьшение величины задержек посредством использования иерархии быстрой памяти; обеспечение работы с памятью со скоростью, определяемой не задержкой выполнения операций, а возможным темпом их выполнения.

Первый подход реализуется введением быстрой кэш-памяти нескольких уровней и разного типа блоков преднакачки данных в быстрые буферные памяти. Однако эти приемы дают эффект лишь для задач с хорошей пространственно-временной локализацией адресов обращений к памяти и их хорошей предсказуемостью, например, для такой задачи, как умножение плотно заполненных матриц. Эта задача характеризуется высокой вероятностью повторного использования данных и предсказуемостью обращений к данным. В то же время для современных задач категории DIC характерно увеличение доли нерегулярной работы с памятью, для которой свойственна низкая вероятность повторного использования данных или непредсказуемость адресов этих обращений в большом пространстве, как например для специального теста GUPS. Несмотря на то что это синтетический тест, полученные на нем характеристики настолько важны, что являются главным улучшаемым параметром (почти на три порядка) разрабатываемых сегодня перспективных суперкомпьютеров будущего, которые составят основной парк стратегических вычислительных средств США после 2010 года.

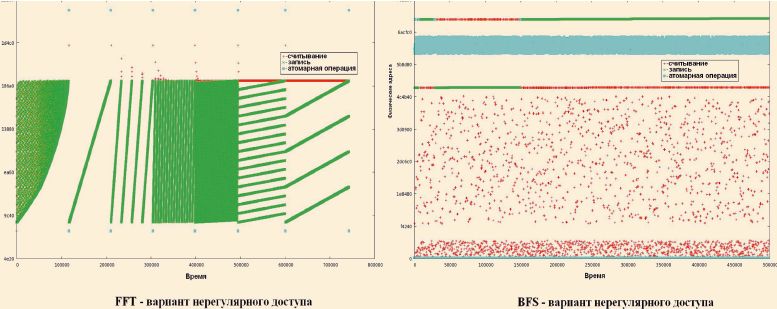

Степень нерегулярности работы с памятью на тесте GUPS — не такая уж абстракция, как утверждают некоторые апологеты вычислительных средств с традиционной архитектурой. На рис. 2 показаны профили обращений к памяти задач быстрого преобразования Фурье (FFT) и задачи поиска вширь на графе (BFS). Излишне напоминать, что первая — это задача из области обработки сигналов и изображений, решаемая, в частности, в изделиях навигации и целенаведения, а вторая — типичный инструмент анализа разведывательных данных, построения систем борьбы с терроризмом и построения сложных систем управления.

В приведенных на рис. 2 профилях каждая точка?— это обращение к памяти по некоторому адресу (ось Y) на некотором такте работы программы (ось X), цвет точки означает тип операции с памятью. Профиль программы с хорошей пространственно-временной локализацией обращений к памяти содержит горизонтальные и наклонные линии регулярного вида. Для DIC-задач на профилях характерна «пурга» — площади, засеянные точками одинакового или разного цвета, что и показано на рис. 2.

Для задач с нерегулярной работой с данными первый метод обеспечения толерантности за счет снижения задержек не подходит, и здесь обычно используется второй подход, суть которого (правило Литтла) в обеспечении при решении задачи выдачи и выполнения большого количества одновременных обращений к памяти и получении за счет этого видимой приложением средней скорости их выполнения, которая определяется не задержкой выполнения каждой операции, а темпом завершения этих операций. Такой тип толерантности обеспечивают векторные процессоры — большое количество обращений получается из-за использования векторных операций. Сейчас к таким устройствам добавились и многоядерно-мультитредовые процессоры — большое количество обращений обеспечивается одновременным выполнением значительного количества «легких» процессов, каждый их которых независимо от других выдает обращения к памяти.

Надо подчеркнуть, что обеспечение толерантности второго типа определяется не только способностью выдачи в процессоре большого количества одновременно выполняемых обращений к памяти, причем не блокируя вычислительный процесс до поступления ответов на эти обращения, — это только первое условие. Вторым и третьим условиями являются, соответственно способность коммуникационной сети между процессором и памятью пропустить требуемое для достижения толерантности количество обращений, а собственно для памяти — одновременно выполнить требуемое количество обращений. Рассматриваемая плата с четырьмя микропроцессорами Barcelona интересна именно тем, что, кроме 16 ядер на плате (первое условие), она обладает четырьмя встроенными в микропроцессоры двухканальными контроллерами памяти (второе условие), а также быстрой коммуникационной сетью в виде двустороннего кольца, образуемого посредством быстрых и реактивных, с малыми задержками, каналов HyperTransport (третье условие). Таким образом, вроде бы налицо наличие всех трех условий толерантности, однако действительно ли упомянутые особенности и есть выполнение трех условий?.

По каким признакам можно обнаружить такую толерантность? Оценим скорость (пропускную способность) выполнения операций с памятью или сетью в разных режимах их использования, но главное — определим зависимость скорости от количества одновременно выполняемых операций. Если при увеличении параллелизма скорость увеличивается, то толерантность есть (правило Литтла). Результаты проведенного оценочного тестирования в полном объеме приведены в [1].

Толерантность к задержкам операций с локальной памятью узла

Первые измерения были проведены на тесте STREAM, применяемом при оценке пропускной способности памяти в режиме регулярного доступа. Известно, что STREAM обладает высокой пространственной и низкой временной локализацией обращений к памяти, однако он очень популярен и важен на практике, поэтому и был использован в первую очередь. Использовались мультитредовые версии этого теста, разные варианты привязки тредов к процессорным ядрам и разные варианты размещения данных в модулях памяти платы. В результате оказалось, что для платы с микропроцессорами Barcelona происходит заметное, в четыре-пять раз, увеличение пропускной способности при увеличении количества используемых тредов до 16. Эта плата обладает свойством толерантности в данном режиме регулярного доступа к памяти, а для платы с микропроцессорами Clovertown этого не наблюдалось.

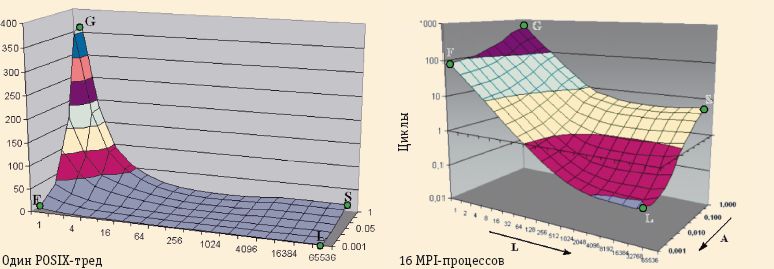

Для оценки работы с памятью в разных режимах использовались две параллельные версии теста APEX-MAP: версия с MPI-процессами и OpenMP-версия с POSIX-тредами. В эксперименте с тестом APEX-MAP исследовалась зависимость среднего количества тактов процессора, приходящаяся на одно обращение к памяти (все обращения на считывание), от изменяемой тестом по некоторой схеме пространственно-временной локализации этих обращений.

На рис. 3 дана APEX-поверхность для одного POSIX-треда, в которой выделены точки G, L, S и А c предельными значениями пространственно-временной локализации (ось L — это изменяемая пространственная локализация, а ось A — изменяемая временная локализация, направление стрелки показывает увеличение локализации). Главный полученный результат для платы с микропроцессорами Barcelona — при увеличении параллелизма (количества тредов до 64) резко уменьшаются задержки в точке G, с 360 тактов до 47. При этом уменьшение происходило даже тогда, когда количество тредов превышало количество ядер процессоров платы. Похожего уменьшения количества тактов для платы с микропроцессором Clovertown не наблюдалось — для одного треда задержка была около 280 тактов, а на 16 тредах — 70 тактов, на этом уменьшение задержки прекратилось.

Уменьшение задержки также произошло в точках L и S, а в точке F — наоборот, произошло даже некоторое ухудшение. Мы объясняем это тем, что точка F имеет высокую временную локализацию, а с увеличением количества тредов повышается конкуренция за разделение ими одного ресурса — кэш-памяти, что и приводит к снижению характеристик.

Обратим внимание на то, что уменьшение задержек произошло при использовании средств параллельной организации программ в виде POSIX-тредов, напрямую работающих с общим адресным пространством, предоставляемым аппаратными средствами исследуемой платы. Использование более тяжелых MPI-процессов, каждый из которых работает со своей локальной памятью и может лишь моделировать доступ в чужую память через аппарат передачи сообщений, к хорошим результатам не приводит. Такой тяжело достающийся параллелизм не позволяет добиться толерантности (рис. 3).

Толерантность к операциям межузловых взаимодействий

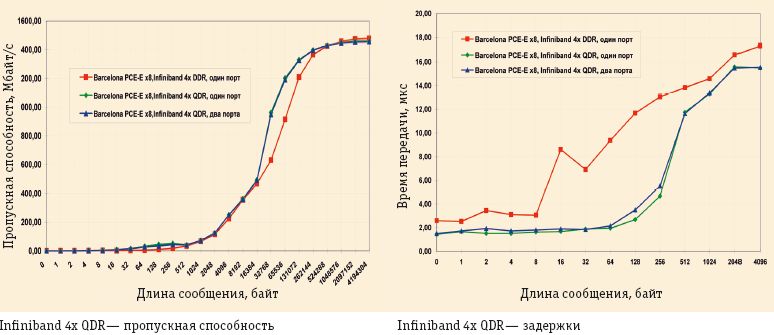

Эффективность работы межузловой сети кластера Barcelona изначально вызывала опасения, поскольку в узлах микропроцессоры работают с одним сетевым маршрутизатором, причем некоторые передают свои данные в него через несколько каналов HyperTransport (рис. 1). Исследования сетевых возможностей производились с использованием пакета PMB (Pallas MPI Benchmark, сейчас — Intel MPI Benchmark), а также теста BISECT (входит в тестовую программу MPPTEST стандартной поставки MPI). Сравнения проводились в основном с кластером МВС 50К, а некоторые из результатов удалось получить для более быстрой сети QDR*.

Для платы с микропроцессорами Barcelona при увеличении пар ядер от одной до восьми бисекционная пропускная способность между двумя узлами заметно увеличивается от 1,5 Гбайт/c до 3,5 Гбайт/с. Это было получено для двухпортового подключения маршрутизатора к коммутатору. Для платы с микропроцессорами Clovertown такой эффект масштабирования бисекционной пропускной способности не наблюдался, ее изменения были с уровня 1,25 Гбайт/с для одной пары до 1,6 Гайт/с для восьми пар. Вместе с тем для платы с микропроцессорами Barcelona 16 взаимодействующих пар оказались слишком большой нагрузкой, и улучшения не произошло, а на сообщениях длиной более 16 Kбайт было зафиксировано даже ухудшение показателей. При работе в сети QDR при увеличении параллелизма до 16 пар наблюдается уверенный рост пропускной способности на пакетах средней длины, хотя предельные значения на длинных пакетах оказались для большого количества пар немного ниже, на уровне 3 Гбайт/c [1].

Сравнение ядер Barcelona и Clovertown

Как отличаются реальные производительности сравниваемых систем не на специальных, а на прикладных оценочных тестах и программах, как влияет на производительность обнаруженная толерантность? Будем вести сравнение с платами, которые вообще не обладают толерантностью (платы кластера МВС 50К с микропроцессорами Clovertown с тактовой частотой 3 ГГц или 2,3 ГГц). Понятно, что развиваемая реальная производительность зависит не только от работы с памятью, но и от качества реализации функциональных устройств. Эти сравнения исследуемого оборудования проводились на пакете тестов Euroben 4.2, модуль mod1ac.

При тестировании применялись группы этих тестов (всего 10 групп), составленные таким образом, чтобы показать ту или иную особенность тестируемого оборудования, причем тесты внутри группы в некоторых случаях выбирались по определенной логике изменения нагрузки с целью выявления дополнительных особенностей объектов тестирования. На рис. 4 показаны характеристики, полученные для одной из этих групп. Группа подобрана так, что от теста к тесту меняется количество арифметических операций, приходящихся на одно обращение к памяти. Видно, что реальная производительность зависит именно от этого параметра. Дополнительно отметим, что одна из особенностей DIC-задач?— малое количество арифметических операций на одно обращение к памяти. Оценочное тестирование на взятой для примера группе тестов (рис. 4), показывает, как негативно это сказывается на реальной производительности.

Качество реализации ядра микропроцессоров Clovertown оказалось выше, чем у Barcelona, но и частота у них выше. Например, на этих тестах одно ядро микропроцессора Clovertown/3 ГГц в полтора-два раза быстрее, чем ядро микропроцессора Barcelona/2,3 ГГц.

Результаты на прикладных тестах

Для тестов пакета газогидродинамических задач NPB 3.1 микропроцессор Clovertown лучше всего работает, когда на 8-ядерной плате загружено только одно ядро, а остальные ядра не используются. Если же загрузить все восемь ядер, то производительность одного ядра может упасть в три раза и более, тогда общая производительность за счет многоядерности повышается лишь в два — два с половиной раза [1].

Разброс реальной производительности при использовании большого количества ядер для платы с микропроцессорами Barcelona оказался меньше. В связи с этим общую реальную производительность в целом с платы удается получить не меньше, а иногда и больше, чем на микропроцессоре Clovertown c большей частотой и лучшими по реализации ядрами. Для иллюстрации на задаче CG из этого пакета на рис. 5 дан типичный пример развиваемой реальной производительности на одно ядро (процессор) в зависимости от количества параллельных процессов и степени загрузки ядер микропроцессоров. Числа над линиями графиков в кружках показывают, сколько ядер на плате загружено (1 — одно ядро из всех имеющихся, 2 — два ядра и т.д.).

Важно отметить, что необходимость достижения требуемой при распараллеливании эффективности за счет отказа от использования ядер на плате приводит к тому, что задействуется большее количество узлов, а это существенно повышает стоимость решения по сравнению со случаем, когда удается эффективно загрузить все ядра платы. Результаты на остальных оценочных программах пакета NPB 3.1 показаны в [1] и приводят к таким же качественным выводам.

При оценочном тестировании рассматривался также тест UA (расчет на неоднородной, перестраиваемой в процессе счета сетке) из новой версии пакета NPB. Микропроцессор Barcelona на этой задаче при загрузке восьми ядер одного узла показывает приблизительно в полтора раза большую реальную производительность в сравнении с восемью ядрами микропроцессора Clovertown/2,3 ГГц. Эта производительность при использовании 16 ядер платы с микропроцессорами Barcelona превосходит восемь ядер Clovertown уже в 2,4 раза.

Сравнения также производились на имитационной модели (синхронная параллельная имитационная модель) системы «Ангара» (компьютер с глобально адресуемой памятью, создаваемый в рамках работы по построению суперкомпьютера стратегического назначения мультитредово-потокового типа). В некоторых вариантах расчетов плата с микропроцессорами Barcelona демонстрирует близкое к линейному ускорение от распараллеливания, причем позволяет работать при эффективном использовании всех ядер узла (такая же ситуация, что и для теста UA). Это важно, поскольку при моделировании полной конфигурации суперкомпьютера из 32 тыс. вычислительных узлов приходится запрашивать для использования 1024 ядра, что при 50-процентной загрузке ядер плат означает запрос 256 вычислительных узлов кластера. Такое системные администраторы и программы планирования прохождения задач разрешают редко, особенно если счет идет много часов. Следует отметить еще одно важное свойство исследуемой платы — большая оперативная память, доступная на узле (64 Гбайт) всем ядрам через глобальную адресацию в пределах узла, что также хорошо сказывается и при решении DIC-задач.

QDR против DDR

Сеть QDR имеет дуплексную пропускную способность 4 Гбайт/с, а имеющийся на плате Supermicro AS-1041M-T2 интерфейс PCI-E 8x — 2 Гбайт/с. Таким образом, подключение такой быстрой сети к медленному интерфейсу изначально странно, и здесь заведомо нельзя было получить более высоких характеристик при передаче длинных сообщений, чем позволяет интерфейс PCI-E 8x. Тем не менее некоторые результаты оказались неожиданными.

На рис. 6 для двух узлов, в каждом из которых используется одно ядро, приведены данные пропускной способности и задержки передачи сообщений в зависимости от их длины на тесте PingPong. Сравнивались сеть DDR c подключением узла к коммутатору через один порт, а также вдвое более быстрая сеть QDR с вариантами подключения узла через один и два порта.

Как и ожидалось, при передаче длинных сообщений улучшения от замены сети DDR на QDR при интерфейсе PCI-E 8x не произошло, однако в двух областях, до 512 байт и в диапазоне 16—256 Кбайт, заметны отличия. Наибольший интерес представляла первая область коротких сообщений, поскольку она определяет степень реактивности сети, что может быть применено, например, при реализации односторонних взаимодействий в MPI-2 либо при программной реализации распределенной общей памяти. На графике зависимости задержек передачи сообщений от их длины (рис. 6) видны низкие значения задержек, меньшие, чем задержки сети DDR почти в пять раз, а ведь теоретически ожидалось, что, в соответствии с тактовой частотой, различия будут не более чем вдвое.

Становится уже почти традиционным сравнение быстро прогрессирующей сети Infiniband cо специальными заказными сетями, прежде всего Cray SeaStar, сетью Cray X1, сетями SGI Altix, IBM и Quadrics. В работе [1] собраны характеристики сетей DDR и QDR, показанные на тестах PingPong и PingPing в сравнении с двумя сетями заказного типа. Заказные сети пока превосходят Infiniband, но по некоторым параметрам разрыв сокращается, хотя и остается достаточно большим. Добавим, что с появлением Cray Baker и Сray BlackWidow этот разрыв опять увеличится, поскольку уже ясно, что появятся сети нового поколения (например, сильносвязная cеть Клоса с адаптивной передачей сообщений на кристаллах Cray YARC), интегрированные с мультитредовыми коммуникационными сопроцессорами (например, Cray Gemini). Такой процесс «ухода» вперед заказного сетевого оборудования и «преследования» его коммерчески доступными сетями будет теперь всегда.

В сравнении с сетью Сray XT4 (заказная сеть, трехмерный тор, использует маршрутизаторы Cray SeaStar2 c шестью линками, дуплексная пропускная способность каждого из которых равна 3,8 Гбайт/с) данные на тесте PingPong соответствуют развиваемой в XT4 пропускной способности лишь в том случае, если снизить частоту линка XT4 в два раза. При полной частоте в XT4 достигается пропускная способность 2 Гбайт/с, задержка на сообщениях менее 16 байт — 5 мкс, а менее 1 Кбайт — около 8 мкс. Данных по более новой сети для Cray XT5 пока нет, но известно, что в ней используется новая реализация маршрутизатора Cray SeaStar2+ c дуплексной пропускной способностью каждого линка 4,8 Гбайт/с. В [1] имеются данные по другим исследованным характеристикам DDR и QDR.

***

Главным результатом оценочного тестирования фрагмента суперкластера с микропроцессорами Barcelona и сетью QDR стало экспериментальное подтверждение наличия у него толерантности к задержкам операций регулярного и нерегулярного доступа к памяти и операций с межузловой сетью. Это позволяет уже не отказываться, как было раньше, от использования при решении задач части ядер, чтобы избежать значительной деградации реальной производительности отдельного ядра. Примечательно, что такая толерантность обнаружена впервые в коммерчески доступных и используемых для создания кластеров аппаратных средствах, однако эта толерантность хуже, чем в уже имеющихся и создаваемых суперкомпьютерах заказного и полузаказного типа.

Полученные результаты позволили сделать вывод о целесообразности создания суперкластера на базе Barcelona (или AMD Shanghaj) и сети QDR для полномасштабного, до 32 тысяч узлов, имитационного моделирования СКСН с целью отработки архитектуры и микроархитектуры, отладки системного программного обеспечения и разработки приложений. Микропроцессоры AMD сегодня не очень популярны в среде отечественных разработчиков кластеров, хотя именно они применяются компанией Cray в полузаказных суперкомпьютерах серии XT, а IBM использует их в самом мощном на сегодняшний день суперкомпьютере Roadrunner. В сентябре 2008 года пришло сообщение из Китая о создании именно на микропроцессорах Barcelona самого мощного в этой стране кластера Dawning 5000 c пиковой производительностью 230 TFLOPS.

Большое количество ядер, наличие эффективных прямых каналов прямого подключения сопроцессоров и прямого соединения кристаллов (AMD HyperTransport и будущий Intel QuickPath) открывают широкие возможности создания суперкластеров, приближающихся по возможностям к младшим моделям суперкомпьютеров. По такому пути, например, пошли на первых порах в проекте DARPA HPCS в США (создание к 2010 году СКСН с реальной производительностью в несколько PFLOPS), в Roadrunner — совместном проекте Лос-Аламосской лаборатории и IBM, а также в проектах создания к 2009 году системы NovaScale (Франция) с пиковой производительностью 300 ТFLOPS и в проекте создания к 2010 году системы Keisoku (Япония) с пиковой производительностью в 10 PFLOPS.

Вместе с тем суперкластеры — тип суперкомпьютеров, находящихся между создававшимися ранее кластерами и будущими СКСН — не способны заменить настоящие заказные СКСН, работы по которым сегодня активно ведутся в развитых странах при мощной государственной поддержке. Задачи класса DIC — один из примеров применений таких систем, и уже имеются сообщения о значительном прорыве в их решении именно благодаря применению СКСН с новой архитектурой.

-

Оценочное тестирование кластера на основе 4-сокетных плат с 4-ядерными микропроцессорами AMD Barcelona, соединенных коммуникационной сетью Infiniband 4X DDR (версия 29 от 16.09.08). Под редакцией Л.К. Эйсымонта. Отчет о НИР. ОАО «НИЦЭВТ», ЗАО «Троник», 2008.

Максим Кудрявцев, Денис Мошкин, Леонид Эйсымонт ({mkudryavtsev,den_m,verger}@nicevt.ru)— сотрудники НИЦЭВТ (Москва), Михаил Полунин (mikep@tronicint.ru) — технический директор компании «Троник» (Москва).

Программа создания перспективных суперкомпьютеров.

Российский суперкомпьютер с глобально адресуемой памятью.

Оценка быстродействия нерегулярного доступа к памяти.

* В статье приведены лишь данные для теста BISECT, а все остальные результаты в полном объеме представлены в [1].