Графические процессоры из ускорителей, выполняющих функции обработки графических примитивов с достаточно ограниченными вычислительными возможностями и программными средствами, ориентированными для работы с графикой, превратились сегодня в универсальные устройства GPGPU (General-Purpose computing on Graphics Processing Unit). Этот процесс начался в 2009 году в результате появления Nvidia Fermi, массово-мультитредового GPGPU. Этот и последовавшие за ним процессоры обеспечивали не только высокую пиковую производительность на уровне десятков TFLOPS для двойной точности (FP64) на один графический процессор, но и повышенную толерантность к задержкам выполнения обращений к памяти и простоям функциональных устройств из-за информационных зависимостей команд по данным, что одновременно позволило достичь и высокую реальную производительность на решаемых задачах.

В таких системах изначально поддерживалась скалярная и векторная обработка, а с появлением в 2017 году GPGPU V100 (Volta) стала поддерживаться обработка плотнозаполненных матриц для нейросетевых алгоритмов. В GPGPU A100 (Ampere), вышедшем в 2020 году, уже поддерживается работа с разреженными матрицами. Современный GPGPU H100 (Hopper, 2022 год) снабжен командами поддержки алгоритмов динамического программирования, используемых в комбинаторных задачах, решаемых методом перебора. Совершенствование архитектуры одновременно сопровождалось накоплением программных средств: математических библиотек, компиляторов, отладчиков, инструментов трассировки программ и автоматического тьюнинга (подстройки) программ для достижения большей эффективности использования аппаратных средств этих сложных процессоров.

Сегодня GPGPU используются в ЦОДах, а также в мощных суперкомпьютерных системах экзафлопсного уровня, развертываемых в бортовых, мобильных или стационарных конфигурациях. Естественно, GPGPU ориентируются не только на высокопроизводительные вычисления (HPC) и задачи искусственного интеллекта, но могут использоваться и для решения собственно задач обработки графики.

Преимущества серверных процессоров AMD EPYC Rome и Milan архитектур Zen 2 и Zen 3 соответственно (а скоро ожидается и Zen 4) над Intel Xeon широко известны, но в области использования GPU для высокопроизводительных вычислений и решения задач искусственного интеллекта господствуют GPGPU от Nvidia и до недавнего времени возможные успехи AMD были малопредсказуемы. Однако с появлением в конце 2020 года графического ускорителя AMD Instinct MI100 ('Arcturus') на базе архитектуры CDNA (Compute Digital Network Architecture) ситуация изменилась — GPGPU от AMD превзошли по пиковой производительности и другим показателям самые мощные на тот момент процессоры V100 и A100 от Nvidia. В следующих моделях GPGPU от AMD семейства MI200 с кодовым названием 'Aldebaran' используется новая архитектура CDNA 2 [1]. Такие процессоры используются, например, в суперкомпьютере HPE Cray Frontier, и именно эти системы планируется использовать в первом на Североамериканском континенте экзафлопсном суперкомпьютере EL–Capitan (2 EFLOPS), ожидаемом в 2023 году для развертывания в Ливерморской лаборатории и предназначенном для выполнения исследований в сфере изменения климата, мутации генов, разработки новых лекарств и разработки новых технологий двойного применения. Однако и Nvidia не стоит на месте — после появления GPGPU H100 на технологии 4 нм с архитектурой Hopper ситуация может измениться.

.jpg) |

| Рис. 1. Общая структура блока CU процессоров GCN. Имеется локальная память LDS с возможностью обработки данных непосредственно в памяти |

.jpg) |

| Рис. 2. Детальная структура блока CU процессоров GCN с выделением 4-канального 40-тредового устройства управления, скалярных и векторных функциональных устройств (матричное устройство не подключено) |

Архитектуры CDNA базировались на архитектуре AMD GCN (Graphics Cores Next), в основе которой — множество вычислительных блоков CU (Сompute Unit) (www.techpowerup.com/gpu-specs/docs/amd-gcn1-architecture.pdf). На рис. 1 и 2 приведена структура такого блока CU в архитектуре GCN [2].

В отличие от GPGPU компании Nvidia, в открытых источниках ('AMD Instinct MI200 Instruction Set Architecture. Reference Guide. 04-February-2022') имеется описание реализуемой аппаратно системы команд AMD Instinct (MI100/MI200) в CU. Структура и микроархитектурные алгоритмы функционирования CU представлены в [1]. В наборе имеется 1812 команд, из них: 364 скалярных (191 вычислительная, 173 — операции с памятью); 1458 векторных и матричных (738 вычислительных, 720 — операции с памятью разного уровня иерархии). Из векторных команд работы с памятью можно выделить: 256 команд с памятью LDS каждого CU, а также с внутрикристальной памятью GDS емкостью 4 Kбайт общей для всех CU процессорного кристалла; 237 — операции с векторами и представлениями изображений из памяти с их преобразованиями «на лету» через кэш-память L1 для векторов в каждом CU; 227 — операции с внекристальной памятью. Примечательно огромное количество атомарных операций и операций синхронизации выполнения команд с информационными зависимостями по ресурсам, включая разного типа барьерные синхронизации. При работе с памятью через векторные регистры поддерживается не только доступ к памяти с регулярным шагом, но и доступ через индекс-вектор (операции gather и scatter).

На самом деле разных реально выполняемых команд в MI100/MI200 значительно больше, поскольку они отличаются не только кодами операций, но и по кодировке операндов, которая имеет множество вариантов. Например, в поле операнда команды возможна кодировка использования скалярного или векторного регистра либо вообще короткой константы.

Каждый блок CU — это 40-тредовое ядро, причем c асинхронными тредами. Для сравнения, Nvidia в мультитредовом ядре предусматривает 32 асинхронных треда. В блоке CU имеются и синхронные треды, они привязаны к каждому асинхронному треду, но не так, как в устройствах Nvidia, где каждый асинхронный тред связан с 32 синхронными CUDA-тредами. В блоке СU синхронные треды введены более естественно — это элементы векторов, с которыми работает асинхронный тред. Вектор содержит до 64 элементов, вдобавок в одном асинхронном треде можно использовать много разных векторов. Такое сочетание мультитредовости и обработки векторов считается перспективным и применяется сейчас во многих современных процессорах.

Что касается микроархитектурных алгоритмов функционирования, то здесь можно отметить лишь, что множество из 40 асинхронных тредов разбито на четыре группы (на рис. 2 — это SIMD0, SIMD1, SIMD2 и SIMD3). Каждая из групп обслуживается по одной за такт, по круговой дисциплине (roundrobin). За такт из одной группы может быть выдано до пяти команд для разных функциональных устройств и из разных асинхронных тредов этой группы. Запуск команд из каждого отдельного треда осуществляется по дисциплине in-order. Всего имеется семь типов разных команд для разных устройств (рис. 1): Branch — команды переходов; MSG unit — команды выдачи/приема сообщений для взаимодействия с другими CU; Export/GDS decode — команды взаимодействия с другими CU через общедоступную память GDS; Vector Memory Decode — векторные команды работы с памятью; Scalar Decode — скалярные команды; Vector Decode — векторные команды; LDS decode — команды работы с памятью LDS конкретного CU.

Накоплен многолетний практический опыт анализа и тестирования процессоров архитектуры GCN, которые оказались привлекательны не только по своим характеристикам, но и по прозрачности архитектуры и микроархитектуры, что важно для оптимального программирования. Этого нельзя сказать про GPGPU от Nvidia, причем на узком классе задач, связанных с информационной безопасностью, процессоры на базе GCN оказались привлекательнее устройств Nvidia, но последние предпочтительны на более широком классе задач. Однако с выходом архитектуры CDNA ситуация изменилась.

В блоках CU архитектуры CDNA появились матричные ядра (аналоги тензорных ядер в GPGPU Nvidia), которые могут выполнять команды MFMA (Matrix-Fused-Multiply-Add) — «умножить-и-сложить» над матрицами маленького размера, причем в множестве разных вариантов и с числами разных типов. Данные для этих ядер берутся с векторных регистров. Такие операции со смешанными типами данных актуальны для задач искусственного интеллекта, а их использование повышает энергоэффективность. В CDNA 2 возможности MFMA были серьезно расширены благодаря поддержке еще и FP64 [1]. Но нужно отметить, что в MI200, в отличие от современных GPGPU от Nvidia, нет аппаратной поддержки работы с разреженными матрицами (см. Таблицу).

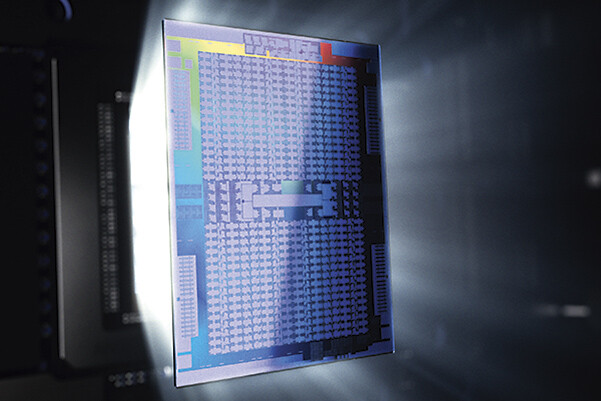

В CDNA 2 на нижнем уровне иерархии блоков используются CU. Два столбца по 14 CU образуют другой блок — CE (Compute Engine). В GPGPU MI200 имеется четыре CE, входящих в кристалл GCD (рис. 3). Семейство GPGPU MI200 включает еще модели MI250 и MI250X, которые используются как бескорпусные (чиплеты) конструктивы в двухкристальных процессорах.

Приводимые разработчиками пиковые значения производительности P в GFLOPS (для HPC обычно имеется в виду формат FP64) у GPGPU можно рассчитать по традиционной формуле P = N × H × 2, где N — общее число потоковых ядер (см. Таблицу), H — частота (ГГц), умножение на 2, что связано с выполнением команды «умножить-и-сложить». Однако производители рассчитывают P для максимально возможной частоты. Но известно, что из-за большого тепловыделения при большой нагрузке эта частота понижается, что для GPGPU с очень большим числом ядер весьма существенно. Поэтому корректнее ориентироваться на производительность, реально достигаемую на тестах или приложениях с учетом доступного тепловыделения. Например, в [3] показано, что MI100 по производительности на тестах иногда опережает V100, но в ряде случаев отстает. Подобных публикаций для MI200 в открытых источниках пока нет, но имеются предварительные данные, где MI200 сопоставляется с A100 [4].

В CDNA 2, как и в GCN, D-кэш L1 для CU локальный, а кэш L2 в GCN был общим для кластера из четырех CU, а теперь четыре CE в одном GCD разделяют общий 16-канальный наборно-ассоциативный кэш L2 емкостью 8 Мбайт. Емкость полного кэша L2 в MI250/MI250X (для двух GCD) также вдвое больше, чем в MI100. Повышенная емкость кэша важна для GPGPU в связи с потенциальной необходимостью в высокой пропускной способности при работе с памятью. В MI250 с двумя GCD суммарная пиковая пропускная способность кэша L2 равна 7 Тбайт/с, что вдвое больше, чем в MI100 [1].

.jpg) |

| Рис. 3. Архитектура CDNA 2 — один кристалл GCD. VCN (Video Core Next) — специальное ядро для кодировки/декодировки видео различных форматов, обеспечивающее ускорение и низкое энергопотребление |

Каждый GCD в CDNA 2 имеет по 64 Гбайт памяти HBM2e (High-bandwidth memory), что вдвое больше, чем в MI100. Пиковая пропускная способность HBM2e (c шириной шины 4096 бит) у одного GCD равна 4096/8 × 1,6 ГГц × 2 = 1,6 Тбайт/с, а в MI250/MI250X, где имеется по два GCD, она вдвое выше и по емкости, и по пропускной способности. Контроллеры памяти (рис. 3) обеспечивают интерфейс между физической памятью и стандартными контроллерами (представлены и блоки Memory Phy, упростившие конструирование).

Крайне важным в MI200 является использование специального межсоединения Infinity Fabric 3.0 (рис. 3) между несколькими GPGPU в сервере, которое может использоваться и для связи между процессором EPYC и MI200. Это межсоединение можно считать расширением PCIe, и его можно использовать с коммутатором [4]. Infinity Fabric похоже на Nvidia NVLink, причем оно не только осуществляет обмен данными между разными GCD, но и обеспечивает когерентность кэш-памяти, что упрощает программирование. При этом когерентность может обеспечиваться между кэшами GCD и усовершенствованными AMD EPYC (например, 64-ядерными 7A53). Каналы Infinity Fabric бывают разных типов, а связь GCD с EPYC может осуществляться и традиционно через PCIe. Восемь внешних каналов от всех GCD в MI250/MI250X к EPYC дают суммарную пропускную способность 800 Гбайт/с, а между GCD в их паре пиковая пропускная способность достигает 400 Гбайт/с, что существенно выше, чем было в MI100 (см. Таблицу).

Важный показатель GPGPU — энергопотребление, и AMD часто приводит соответствующие данные для всей видеокарты TBP (Total Board Power), но важнее то, что MI250/MI250X предполагают работу с новым форм-фактором OAM (Open Accelerator Module), поддерживаемым ведущими производителями. С OAM планируется и работа будущего графического процессора Intel Ponte Vecchio, для которого ожидается энергопотребление на уровне 600 Вт и в оборудовании HPE c MI250X в суперкомпьютере Cray Frontier. В Nvidia H100 планирует продолжить применение своего форм-фактора SXM — SXM4 в A100 и SXM5 в H100.

По ряду характеристик производительности процессоры AMD MI200 имеют преимущества относительно устройств Nvidia, но для создания на MI200 реального приложения понадобятся специальные открытые программные средства — Radeon Open Compute (ROCm, www.amd.com/en/graphics/servers-solutions-rocm), а драйвер для MI200 имеется в ядре Linux 5. Для низкоуровневого программирования с применением CUDA в GPGPU Nvidia AMD предлагает замену — HIP (Heterogeneous Interface for Portability). Для MI200 поддерживаются возможности работы с OpenCL и OpenMP. В рамках проекта GPUFORT разрабатываются средства автоматической конвертации с CUDA Fortran и OpenACC на поддерживаемые ROCm возможности (github.com/ROCmSoftwarePlatform/gpufort). Предлагается также и набор математических библиотек (BLAS, FFT и др.). Сейчас доступна версия ROCm 5.1.1, однако пока еще нет опыта применения ROCm на GPU семейства MI200, показывающего реальную производительность в тестах и приложениях.

Самые мощные суперкомпьютеры сейчас обычно используют GPGPU в своих узлах, достигая высокой энергоэффективности, а в самих GPGPU при этом используются и самые быстрые технологии памяти. Но надо иметь в виду, что яркие успехи в производительности наблюдаются обычно в определенных приложениях. Например, большое ускорение достигается при использовании GEMM (умножение матриц) в лимитирующей время выполнения стадии или на задачах искусственного интеллекта. Но для большинства HPC-приложений для получения высокой производительности c использованием GPGPU требуются дополнительные исследования. При добавлении GPGPU в состав сервера его цена существенно увеличивается, что может быть не всегда адекватно росту производительности приложения. С другой стороны, учитывая, что продукция AMD традиционно отличалась демократичной ценой, появление систем на базе CDNA и CDNA 2 способствует привлекательности GPGPU. Однако MI200 массово пока не поставляются и ориентироваться по стоимости можно лишь по сборке с ними суперкомпьютера Frontier, хотя определенные предположения о возможных ценах MI250X можно найти в [4].

Другой важный вопрос — для GPGPU требуется специализированная система программирования. Задача переноса программного обеспечения c GPGPU от Nvidia на MI200 пока не исследована. Вероятно, будет расти использование в таком программировании универсальных, теоретически не зависящих от GPGPU программных средств, возможно и OpenMP.

Неизбежность новых архитектур: эволюция и прорыв

Тема разработки мощного и достаточно универсального отечественного ускорителя типа GPGPU неоднократно поднималась на протяжении десятилетия, в результате были созданы лишь специализированные СБИС для конкретных областей применения. В условиях внешнеэкономических ограничений создание мощного отечественного процессора-ускорителя приобрело особую актуальность — подобные процессоры должны на порядки усилить возможности отечественных серверных процессоров семейств Эльбрус и Байкал в суперкомпьютерных системах разного уровня производительности и назначения.

Разработка GPGPU требует решения ряда проблем, поскольку достижение производительности на уровне сотни TFLOPS на числах FP64 и затрат менее 20 pJ (пикоджоуль) на FLOPS с FP64 находится сегодня на пределе физических возможностей существующих технологий. В этой связи особенно важен выбор архитектуры и микроархитектуры, а также соответствующего системного ПО. Класс таких процессоров в целом относится к семейству сверхвысокоскоростной электронной компонентной базы, работы над созданием которой приобрели сегодня особую актуальность.

AMD Instinct позиционируется разработчиком как процессор-ускоритель экзафлопсной эры, а GPGPU от Nvidia, во всяком случае V100 и A100, принадлежат эре петафлопсных компьютеров. Например, в суперкомпьютере El-Capitan (2 EFLOPS) для Ливерморской лаборатории разработчики ориентируются на AMD Instinct, заменяя использованные в его прототипе — суперкомпьютере Perlmutter (5-е место в Top500 ноября 2021 года) Nvidia A100.

Суперкомпьютер EL–Сapitan планируется к выпуску в 2023 году, но экзафлопсный барьер на задаче Linpack (Тест HPL) был преодолен еще весной 2021 года на двух китайских системах: Tianhe-3 (NUDT, National University of Defense Technology) — достигнутая реальная производительность 1,3 EFLOPS или 76% от пиковой производительности; Sunway Ocean Light — достигнутая реальная производительность 1,05 EFLOPS — 79% от пиковой производительности. В этих суперкомпьютерах GPGPU не использовались, хотя у разработчиков имеется свой вариант такого процессора-ускорителя.

AMD Instinct, как и другие процессоры-ускорители семейства сверхвысокопроизводительной электронной компонентной базы, за счет применяемых архитектурных и микроархитектурных решений позволяют преодолеть четыре фундаментальные «стены» [1]: стена памяти, стена энергетики, стена проблемы локализации вычислений на данных, стена низкой масштабируемости производительности при увеличении объемов обрабатываемых данных.

Кроме выполняемых сегодня во всем мире работ по архитектуре и микроархитектуре процессоров-ускорителей, огромное внимание уделяется новым моделям организации параллельных программ. Модели параллельных программ развиваются от статических вычислительных графов потоков данных к динамическим графам, для которых вычислительные процессы порождаются в процессе выполнения. Соответственно, подобные задачи требуют новой архитектуры процессоров — новых команд взаимодействия процессов и аппаратной поддержки специфических структур данных, ранее реализовавшихся лишь программно.

Как и в любой новой области исследований, в сфере GPGPU могут возникать завышенные ожидания от применения тех или иных технологий, например акцентирование на архитектуре RISC–V [2] — едином и открытом наборе команд для всех типов систем от микроконтроллеров до высокопроизводительных систем. Неочевидно, что реализация именно этой системы команд в процессорах-ускорителях решит проблемы создания мощного отечественного процессора-ускорителя. Достаточно сравнить число команд в RISC-процессорах с количеством команд процессоров для реального применения. В AMD Instinct только отличающихся по кодам операций имеется 1822 команды, а в других современных процессорах их еще больше. Например, в Qualcomm Cloud AI 100 для решения задач искусственного интеллекта 2625 команд, из них: 1800 скалярных, более 700 векторных и 125 команд для работы с матрицами. Формат команд как в практических процессорах, так и RISC–V соответствует концепции «load/store», однако одна специализированная команда в реально применяемых сегодня RISC-процессорах аппаратно реализует множество сложных действий, которые соответствуют десяткам или сотням команд RISC–V, что означает, как минимум, снижение производительности и энергоэффективности.

Справедливости ради следует упомянуть процессор ET-SoC-1 от Esperanto Technologies, который представляется как первый высокопроизводительный процессор архитектуры RISC–V с высокой энергоэффективностью, рассматриваемый в компании «Байкал-Электроникс» как возможный вариант создания прототипа процессора-ускорителя. Даже главный конструктор ET-SoC-1 Дэвид Дитцел с достаточным чувством юмора говорит об этом изделии как о процессоре с архитектурой RISC–V, опираясь на «утиный тест» («Если нечто выглядит как утка, плавает как утка и крякает как утка, то это, вероятно, и есть утка»).

Выполняемые во всем мире разработки процессоров-ускорителей можно разделить на три группы: GPGPU (где сегодня лидируют Nvidia и AMD) — это эволюционирующие уже более десяти лет мультитредовые процессоры, обрастающие новыми группами команд и усовершенствованиями микроархитектуры; специализированные процессоры в виде FPGA или специализированных СБИС от крупных производителей, например, Xilinx, Intel, IBM, Google, Amazon и др.; процессоры-ускорители, изобретаемые небольшими стартапами [3]. Имеется еще одна, специфическая группа процессоров-ускорителей — изделия, создаваемые в проектах силовых ведомств. По уровню революционности применяемых решений эти группы можно было бы упорядочить от первой до четвертой. Конечно, революционность — не самоцель, однако более революционная архитектура позволяет лучше и эффективнее решить фундаментальные проблемы «стен».

Важно учитывать деление процессоров-ускорителей на группы и оценивать характер принимаемых в них решений, в противном случае возникает эклектичность в планировании и выполнении отечественных проектов создания сверхвысокоскоростной электронной компонентной базы. Продвижение здесь есть, но медленное — сначала превалировала убежденность воспроизведения для решения задач искусственного интеллекта отечественных матричных устройств-ускорителей выполнения нейровычислений, и эта задача успешно решается; затем родилось мнение, что все-таки требуется процессор-ускоритель типа GPGPU (например, подобный A100), задача поставлена и начата подготовка к ее решению; вероятно, пришло время обратить внимание и на задачу создания отечественных процессоров, конкурирующих с некоторыми образцами из группы стартапов и группы процессоров для силовых ведомств. Сегодня имеется ряд подобных разработок, например появившийся еще в 2019 году многотайловый процессор COLOSSUS Mk с 7-тредовыми ядрами (6 прикладных + 1 системный) в тайлах (базовый компонент процессора), большой суммарной внутрикристальной памятью тайлов и мощной внутрикристальной коммуникационной сетью между тайлами, с десятью мощными внекристальными портами. Известны две успешные реализации этого процессора: Mk1, 16 нм, 1236 тайлов, 304 Мбайт внутрикристальной памяти; Мк2, 7 нм, 1472 тайла, 900 Mбайт памяти. В 2022 году будет готова реализация Mk3, 3нм, 1782 тайла, 2 Гбайта внутрикристальной памяти – вариант для нового суперкомпьютера NUDT и пример попадания из третьей группы в четвертую.

Исключительно интересны на предмет возможностей применения процессоры-ускорители из второй и третьей группы. Например, в конце 2021 года появились сообщения о двух новых проектах в Аргонской и Ливерморской лабораториях, посвященных созданию инфраструктур и проведению масштабных исследований по использованию процессоров-ускорителей для задач искусственного интеллекта, предназначенных для «усиления» уже имеющихся суперкомпьютеров, решающих задачи в области термоядерной энергии, материаловедения, 3D-печати, биологии и медицины. В Аргонской лаборатории был организован тестовый полигон, включающий изделия Cerebras (процессор CS-2), SambaNova (RDU), Groq (TSP), Graphcore (Colossus Mk1), Habana/Intel (Gaudi, Goya). В Ливерморской лаборатории изучались изделия Google, IBM, Nvidia, HPE и AMD, Cerebras и SambaNova.

Что касается разработки отечественного GPGPU, то следует обратить внимание на AMD Instinct, позиционируемый как процессор-ускоритель экзафлопсной эры и по структуре блока CU напоминающий скалярно-векторное ядро NeuroMatrix nmc4 серийного процессора-ускорителя NeuroMatrix NM6408MP (1879BM8Я). В конце октября 2020 года появились сведения о процессоре-ускорителе из четвертой группы — Intel PIUMA (программа DARPA HIVE), представляющего собой универсальный решатель для задач искусственного интеллекта, эффективно работающий с большими графовыми структурами данных, но на три порядка энергоэффективнее всех существующих GPGPU. Процессор должен появиться в конце 2022 года. Данная разработка базировалась на архитектуре массово-мультитредового суперкомпьютера Сray XMT, но подход к реализации мультитредовости в PIUMA был революционно изменен, что вполне можно считать прорывом. Известно, что процессорами такого типа занимаются в Qualcomm и HPE. Проекты, подобные Cray XMT, выполнялись в России и Китае, где в NUDT были доведены до реального суперкомпьютера «Удар грома».

В 2021 году велись организационные работы по проекту IARPA AGILE — в конце января 2022 года были собраны заявки от возможных исполнителей. Речь идет о процессоре-ускорителе с принципиально новой архитектурой, создаваемой «с чистого листа». Ставится задача не только обеспечения эффективной обработки больших массивов неоднородных данных, представленных графами, но и реализация нейросетей, работающих в неэвклидовом пространстве (над графами). Почти все существующие нейропроцессоры работают в эвклидовом пространстве — с массивами чисел. Неизвестно, какая именно архитектура будет соответствовать такой задаче, но очевидно — здесь будут применяться неординарные технологии, что заметно уже в процессорах типа Intel PIUMA: технологии 3D-сборки, нанофотоника с внутрикристальными и внекристальными волноводами с передачей данных одновременно на разных длинах волн.

В современных условиях ограничений необходима мобилизация в области исследований и разработки отечественной сверхвысокоскоростной электронной компонентной базы с координацией действий всех специалистов из промышленности и академической среды. При правильном целеполагании работы в области процессоров-ускорителей дадут результаты.

Литература

1. Леонид Эйсымонт, Павел Забеднов, Павел Зотов. Модернизация и стратегические ИТ // Открытые системы.СУБД. — 2010. — № 3. — С. 24–28. URL: https://www.osp.ru/os/2010/03/13001873 (дата обращения: 21.05.2022).

2. Владимир Фролов, Владимир Галактионов, Вадим Санжаров. RISC–V: стандарт, изменивший мир микропроцессоров // Открытые системы.СУБД. — 2020. — № 2. — С. 30–34. URL: https://www.osp.ru/os/2020/02/13055471 (дата обращения: 22.05.2022).

3. Джон Вервей. «Мозги» для искусственного интеллекта // Открытые системы.СУБД. — 2022. — № 1. — С. 6–11. URL: https://www.osp.ru/os/2022/01/13056118 (дата обращения: 24.05.2022).

—Леонид Эйсымонт (verger-lk@yandex.ru) — член редакционного совета журнала «Открытые системы.СУБД» (Москва).

***

По важным для оценки производительности пиковым показателям MI250/MI250X превосходят доступные на сегодня процессоры Nvidia, но на уровне тестов и приложений соответствующих данных в доступных источниках пока нет. При этом ситуация может поменяться после выхода Nvidia Hopper, однако и AMD не будет стоять на месте — имеются сведения о MI300 c CDNA 3 и четырьмя графическими чиплет-кристаллами.

Важен вопрос переноса приложений для GPGPU компании Nvidia на AMD MI100/MI200. Решение может быть проще для приложений, базирующихся на таких универсальных средствах, как OpenACC, OpenCL или OpenMP, — с учетом обострения конкуренции GPGPU разных архитектур актуальность этих средств может вырасти. Что касается приложений, работающих c CUDA, то объем соответствующей части кода в приложениях может оказаться небольшим, однако оценка простоты перехода с CUDA на HIP с сохранением высокой производительности еще требует тщательного изучения, причем тут могут пригодиться и средства GPUFORT.

В сфере применения GPGPU для задач искусственного интеллекта помимо Nvidia, AMD и Intel работают еще и стартапы. Наиболее известные — СOLOSSUS, CEREBRAS, Goya, Groq, Samba Nova. Не отстают и силовые структуры: проект DARPA HIVE (Hierarchical Identify Verify Exploit), где предложен процессор Intel PIUMA для работы с большими графами (выпуск ожидается в 2022 году); IARPA AGILE (Intelligence Advanced Research Projects Activity Advanced Graphic Intelligence Logical Computing Environment) — процессор с принципиально новой архитектурой для работы с графами и нейросетями над ними.

Литература

1. Introducing AMD CDNA 2 architecture, URL: https://www.amd.com/system/files/documents/amd-cdna2-white-paper.pdf (дата обращения 21.05.2022).

2. Haibo H. Open CL programming and optimization — Part I. Presentation, 113 slides, October 2013, https://free.eol.cn/edu_net/edudown/AMDppt/OpenCL%20Programming%20and%20Optimization%20-%20Part%20I.pdf.

3. Abdelfattah A. et al. GPU algorithms for efficient exascale discretizations // Parallel Computing. — 2021. — Т. 108. — С. 102841.

4. Morgan T. P. Stacking Up AMD MI200 Versus Nvidia A100 Compute Engines, 2021 https://www.nextplatform.com/2021/12/06/stacking-up-amd-mi200-versus-nvidia-a100-compute-engines.

Михаил Кузьминский (kus@free.net) — старший научный сотрудник, Институт органической химии РАН (Москва).

DOI: 10.51793/OS.2022.85.66.002

.jpg)